FoWLP & EMI 차폐기술 콘퍼런스

| FoWLP & EMI 차폐기술 콘퍼런스 | |

| 2016년 11월 24일 (목) 10:00 ~ 16:30 | |

| 강남 리츠칼튼호텔 | |

| 반도체 구매, 설계, 생산 분야 및 완성품 시스템 업계 | |

| 선착순 200명 | |

|

사전등록 : 165,000원 현장등록 : 198,000원 (VAT포함) |

행사명 |

FoWLP & EMI 차폐기술 콘퍼런스 |

|

일 정 |

2016년 11월 24일(목) 오전 10시 ~ 오후 4시 30분 |

장 소 |

강남 리츠칼튼호텔 |

규 모 |

선착순 200명 |

참가비 |

사전등록 16만 5천원, 현장등록 19만 8천원 |

주 관 |

|

| 10:00~10:25 | ||

|---|---|---|

| 10:25~10:30 | 한국반도체연구조합 | |

| 10:30~11:10 | Advanced Packaging Technology 최근의 반도체 패키지들의 동향이 ICT기반 기술의 발전에 따라 고집적, 고효율을 달성하기 위한 시스템 일체화를 위하여 활발하게 연구 개발되고 있다. 하지만 이와 같은 하드웨어 기반의 기술들은 지난 20년간 개발되어 온 수많은 패키지 공정 및 소재 기술들의 융합을 바탕으로 이끌어 온 것으로 과거의 개발 기술들과 이를 바탕으로 새롭게 열리는 시장인 FOWLP나 2.5D IC등과의 연결고리를 알게 되면 의외로 손쉽게 기술동향을 파악할 수 있게 된다. 본 강의는 그동안 개발되어 온 기술적 내용들을 흐름에 맞추어 정리하고 향후의 시장을 예측하여 본다. | 강남대학교 김구성 교수 |

| 11:10~11:50 | 삼성의 차세대 PKG 기술개발 동향 기존 반도체는 Moore's Law에 따라 Front End의 미세화를 중심으로 기술개발되었으나, Front End가 물리적 한계에 봉착하면서 "More than Moore"를 위한 Back End의 개선Needs가 증가되고 있습니다 | 삼성전기 배광욱 상무 |

| 11:50~13:00 | ||

| 13:00~13:30 | FoWLP 패키징 77GHz 레이더 센서의 성능과 혁신 오토모티브 레이더 센서 시장의 등장배경과 그에 따른 NXP의 반도체 솔류션에 대해 먼저 알아보고, NXP의 레이더 센서 제품 로드맵을 통해, bare die솔류션에서 패키징된 레이더 센서로의 시장 이동을 살펴봅니다. 또한, 오토모티브 레이더 센서 마켓에서 요구하는 패키징 기술과 그러한 요구대응을 위한 NXP의 패키징 기술, 즉, FoWLP기술의 종류인 RCP(Redistributed Chip Package)와 eWLB(embedded Wafer Level Ball grid array) 소개, 그리고 이를 활용한 레이더 센서 디바이스, 패키지 성능 등을 설명합니다. | 엔엑스피 반도체 박주양 상무 |

| 13:30~14:00 | Fan Out WLP as Emerging Packaging Technology for High Performance & Device Integration Fan Out Wafer Level Packaging 기술은 반도체 제품의 다양성, 소형화 및 급변하는 시장 변화에 대응할 수 있는 기술로 최근 각광 받고 있다. 동시에 여러 종류의 반도체 소자를 동일 패키지 안에 내장할 수 있는, 이른 바 System In Package를 종래의 기판 등을 사용하지 않고 구현함으로써 특성향상과 더불어 개발 기간 단축, 소형화 및 Sub module 로써의 부품 platform 이 제안될 수 있다. 본 강연에서는 Fan Out Packaging 기술이 패키징 분야 및 나아가 반도체 부품 시장에 기여 할 수 있는 바를 논의한다. | 네패스 김종헌 상무 |

| 14:00~14:30 | ||

| 14:30~15:00 | Advanced Packaging 의검사기술동향 -Fan Out WLP를중심으로 2000년대 초반까지만 하더라도 다양한 반도체 시장보고서 향후 전망코너 - “미래의 Advanced Packaging Roadmap”-에서나 발견할 수 있었던 복잡한 구조의 Advanced Packages 들… FOWLP( Fan Out Wafer Level Package ), SiP(System In Package) PLP(Panel Level Package), Embedded PCB 등등 Advanced Packaging기술을 적용한 패키지들은 어느새 우리가 실생활에서 매일 사용하고 있는 스마트폰, 다양한 웨어러블IoT기기들, 노트북, 태블릿PC, 자동차의 ECU유닛 등에 실제로 적용되고 있고 그 범위를 빠른 속도로 넓혀가고 있다. | 인텍플러스 최이배 사장 |

| 15:00~15:30 | 어드밴스드 반도체 패키징 설계 방법론 전통적인 패키징은 반도체와 PCB를 결합해주는, 반도체 보호 또는 연결의 기능으로 시스템의 기능에는 크게 기여하지 않고 있었다. 그러나 현재의 패키징은 SiP(System in Package), PoP(Package on Package) 등 구조적으로도 복잡할 뿐만이니라 시스템의 성능, 가격 등 그 비중이 점차 커지고 있다. 더우기 FoWLP라는 패키지 설계, 제조 기술에는 패키지에서 요구되는 기능외게 반도체에 적용되는 기능이 필요하게 되었다. | 케이던스코리아 이재호 부장 |

| 15:30~16:00 | 메모리 업계의 EMI 차폐 기술 과제와 해결 방안 현재, 많은 회사들이 EMI 문제가 발생하면 비교적 간단한 System Level에서의 PCB 수정, De-Cap 위치/용량 변경, Shield can 수정, Absorber 부착 등의 방법을 사용하고 있지만, Tablet이나 Smartphone 같은 고집적/고성능 휴대기기에서는 난이도와 비용 증가로 Component level에서의 적극적인 대책을 요구하는 빈도가 증가되는 추세이다. 또한 고안전/고신뢰성을 요구하는 전장용 부품에 대한 인증을 강화하고 있다. 총 588 개의 주요 사항을 기존의 개발 Process에 추가 또는 통합 하도록 요구하는 ISO 26262 기능 안전 표준이 시행되고 있고, ISO 26262에 IEC61967 및 IEC62132 Spec.이 적용되어 있다. 특히, 첨단 안전장치와 편의장치 등이 자동차에 접속됨에 따라 다양한 전자장치를 제어하기 위하여 각종 정보(온도, 압력, 속도 등)를 측정하는 센서와 엔진, 트랜스미션 및 전자 제어장치, 구동장치 등에 많은 반도체가 사용되는 자동차의 경우, 오동작을 일으킬 경우, 인체에 해를 끼칠 수 있으며, 통신기기에 적용된 반도체 부품이 전자파에 의하여 Wi-Fi/GPS/LTE 등 무선통신대역의 수신감도에 영향을 주어서 통화 단절 같은 현상을 발생시키기도 한다. 이에 따라 반도체 업계에서 전자파 발생(EMI)을 줄이고 전자파 영향(EMS)을 적게 받기 위한 연구/개발하고 있는 여러 방법중의 하나인 Conformal shielding과 Component Level 분석을 위해 적용하고 있는 Near Field Scan의 효용성을 설명하고, Robust Design을 위한 Modeling 기법을 소개한다. Conformal shielding은 반도체 Package 외곽을 금속으로 덮는 것으로 Sputter와 Spray 방식을 이용하며, Sputter 방식의 경우 Apple에서는 iPhone6부터 채용하기 시작했음을 Teardown 자료를 통해 확인 할 수 있다. Spray 방식은 기본적인 특성을 만족시키는 정도까지 개발이 완료되었고, 생산성과 차폐특성 최적화를 위한 단계에 있다. 이러한 소자들의 차폐특성을 분석하는 방법중의 하나가 Surface Scan Method(Near Field Scan)이다. Near Field Scanner에 연결되는 장비에 따라 EMI/EMS 분석이 가능한 상용화된 장비들을 이용하면 Conformal shielding 및 Non?Shielding 소자의 Noise Level의 차이를 확인할 수 있으며, 가장 높은 Noise를 발생시키는 위치를 찾아 On/Off-Chip에 대한 설계적 대책 수립이 가능하다. | SK하이닉스 이필수 팀장 |

| 16:00 ~ 16:30 | Wrap-up | 한국반도체연구조합 |

※ 프로그램은 주최측 사정에 따라 변경될 수 있습니다.

| 참석대상 | 반도체 구매, 설계, 생산 분야 및 완성품 시스템 업계 |

|---|---|

| 등록비 (vat포함) |

사전등록 (~11월 23일) : 165,000원 현장등록 (11월 24일) : 198,000원 |

| 사전 등록 마감 | 2016년 11월 23일 (수) 17:00 |

| 결제방법 | 카드결제(법인카드 가능), 온라인 입금 및 쿠폰인증 |

| 송금계좌 | 우리은행 687-106662-13-001 (예금주 : (주)전자신문사) |

| 기타안내 | ▣ 참가비 안내 : (등록 문의처 : 전자신문 정보사업국 02-2168-9333,9338) ▣ 제공내역 : - 교재, 식사/커피, 주차권 |

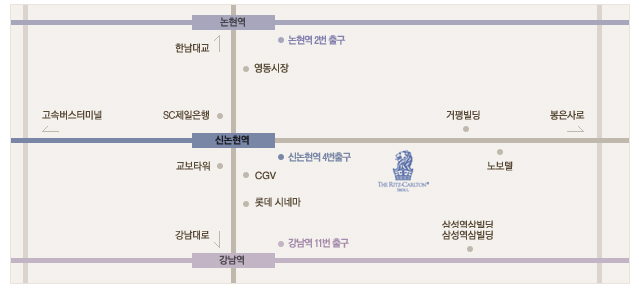

▣ 장소 : 강남 리츠칼튼호텔

※ 상기 정보는 사정에 따라 변경될 수 있습니다.

서울특별시 서초구 양재대로2길 22-16 호반파크 1관, 9층 정보사업국

행사문의 : 02-2168-9338 ㅣ 대표전화 : 02-2168-9200 ㅣ 회사명 : (주)전자신문사 | 대표자명 : 강병준 | 사업자 등록번호 : 547-86-02501

Copyright © The Electronic Times Co., Ltd. All Rights Reserved.